在信息安全行业,美国一直处于集成电路IP核[1-6]的垄断影响力,近年来,美国对华“断贷”事情越来越激烈,“zte中兴”、“华为公司”事情等美对华统治行径也再度让全球对焦到处理芯片等CPU有关的信息安全行业[7]。

现阶段在安全领域,加密技术[14-17]关键根据硬件软件方法设计方案完成,在其中手机软件易受机器设备限定且较不稳定,非常容易减少传输数据品质,而根据设计方案专用型处理芯片的方法完成加密技术是现阶段信息安全行业的流行,该办法更容易置入,适用进行繁杂作用,IP核重复使用性强,具备可靠性高、高数据加密速度、整体费用较劣等优势[7]。

文中主要是详细介绍根据FPGA(Field Programmable Gate Array,当场可编门阵列)的一种AES(Advanced Encryption Standard,高級数据加密规范)优化算法的流水线结构设计方案,并进行其作用认证与特性评定[7-8]。

1引 言

1.1选题背景和实际意义

美国我国标准局于1977年将DES[15](Data Encryption Standard,数据库加密规范)明确为FIPS(Federal Information Processing Standards,联邦政府信息资源管理规范),接着将DES运用于各个领域。伴随着密码破译技术性[16]的飞速发展,DES的稳定性与应用前景遭遇非常大的挑戰,科学研究人员证明选用DES加解密不会再是可以信赖的优化算法,因而,国际性普遍必须制定一个安全级别更高一些、公布的、完全免费的加密技术-AES[14,30](Advanced Encryption)来适用各种信息内容比较敏感行业。NIST(National Institute of Standards and Technology,美国国家行业标准技术性科学研究组织)于1997年向全球征选新一代的加密技术,该优化算法需达到如下所示(如下图1.1所显示)标准:

图1.1 新一代加密技术需符合的标准

2000年,来源于丹麦的Joan Daemaen 和Vincent Rijmen以Square优化算法为原型图的Rijndael优化算法根据最后评比。2001年,NIST将Rijndael设计方案的AES优化算法公布于FIPS PUB 197[14],第二年变成新一代美国美国联邦政府的区块链数据加密规范,从2006年起,AES广泛运用到于各个领域[7],该优化算法具有下列优势:

1)在不一样自然环境中(有没有意见反馈)硬件软件完成后的特性主要表现出色。

2)较短的密匙扩展時间。

3)应用较小的运行内存就可以完成该优化算法,合适在运行内存较小的条件中应用。

4)抗战斗能力强。

5)内部结构循环结构有利于命令级并行处理CPU提高特性。

1.2研究意义

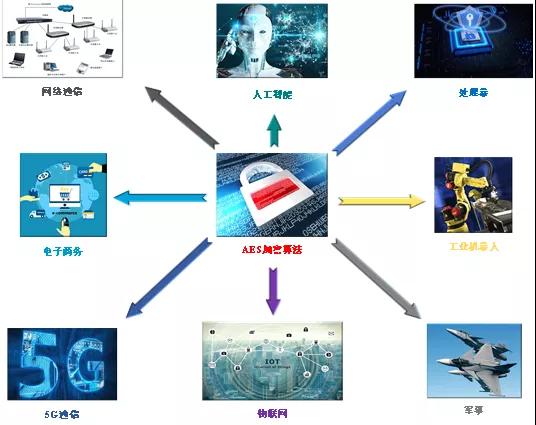

图1.2 AES加密技术主要用途

如下图1.2,现如今互联网技术快速发展趋势,加上WiFi与手机蓝牙的费用与功能损耗慢慢减少,智能穿戴设备与智能家居系统极其普及化,顾客愈来愈经常地开展线上电子支付、移动电商、通讯等日常事务管理,因而很多的关键信息会根据各种各样互联网与移动智能终端等通讯设备开展传送。但在互联网产生高效率方便的与此同时,个人数据的安全隐患也随着加重,为防止个人数据遭到犯罪分子的盗取与进攻,除开在系统方面要开展安全防御外,更要高度重视硬件配置方面的安全防御。因而对CPU硬件加密效率与安全系数的提高,是CPU数据库安全层面必不可少的一部分[7, 23-28]。

在CPUCPU等硬件设备行业,伴随着美国加州大学伯克利分校对RISC-V[7,14]指令系统的开源系统,一个减少门坎的精简指令集的CPU设计方案,例如美国加州大学伯克利分校的BOOM[18-19]、英国剑桥大学的LowRISC[20]、苏黎世联邦政府理工大学与西班牙博洛尼亚大学的PULPino[21]、俄国的RISC-V VHDL[22]等相似的CPU,必定会在5G高速通信行业、AI(人工智能技术)、工业机械手、IOT物联网技术、智能化自动化技术乃至国防安全等行业大规模运用,此外这种CPU的信息安全问题也势必会引发客户的高度重视[7]。

2AES优化算法基本原理

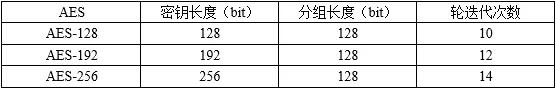

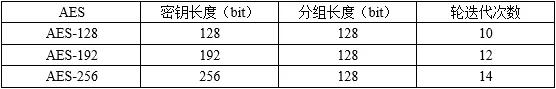

AES加密技术(又被称为Rijndael优化算法)选用对称性登陆密码体系,密匙分成128bits/192bits/256bits三种长短,通称为AES-128/AES-192/AES-256(如表2.1)。该优化算法应用SP构造(取代/换置),密匙长短分成128bits、192bits、256bits三种方式,数据加密全过程的轮函数公式由4层构成(字节数更换、行偏移、列搞混、轮密匙加),在其中S-box应用有限域上GF()的乘除法逆运算,使其具有良好的线形误差与差分信号匀称性[7,14]。

此章简略介紹了AES的优化算法中涉及的主要参数等、数据加密全过程、密匙扩展等。

表2.1 AES三种方式下相应的密匙长短、分类长短、梯度下降法频次

2.1 AES优化算法中主要参数、标记解析函数详细介绍

SubBytes( ):应用对每一个情况引流矩阵中字节数单独使用的最优控制字节数更换表(S-box)进行对情况引流矩阵中的登陆密码变换。

ShiftRow( ):根据用不一样的偏移循环系统挪动情况引流矩阵的最终三行来进行情况引流矩阵的登陆密码变换。

Mixcolumns( ):列搞混,是数据加密全过程中的变换流程,它获得情况引流矩阵的全部列并混和他们的数据信息(彼此之间单独)以转化成新列。

AddRoundKey( ):轮密匙加,在AES数据加密/破译的历程中,根据轮数据信息与轮密匙的异或运算,进行情况引流矩阵的搭建时, 在其中情况引流矩阵与轮密匙长短相同。

XOR:异或运算实际操作,运算符为 。

。

InvsubBytes( ):破译全过程中的变换,即SubBytes( )的逆变换。

InvShiftRows( ):破译全过程中的变换,即ShirtRows( )的逆变换。

InvMixColumns( ):破译全过程中的变换,即MixColumns( )的逆变换。

RotWord( ):在轮密匙扩展全过程中采用的函数公式,它接纳一个四字节数的字并实行循环排列。

Rcon [ ] : 轮变量定义,Rcon[j]为一个字,j为轮空,如表2.2所显示:[7,14]

表2.2 轮变量定义Rcon[j]

2.2数据加密全过程

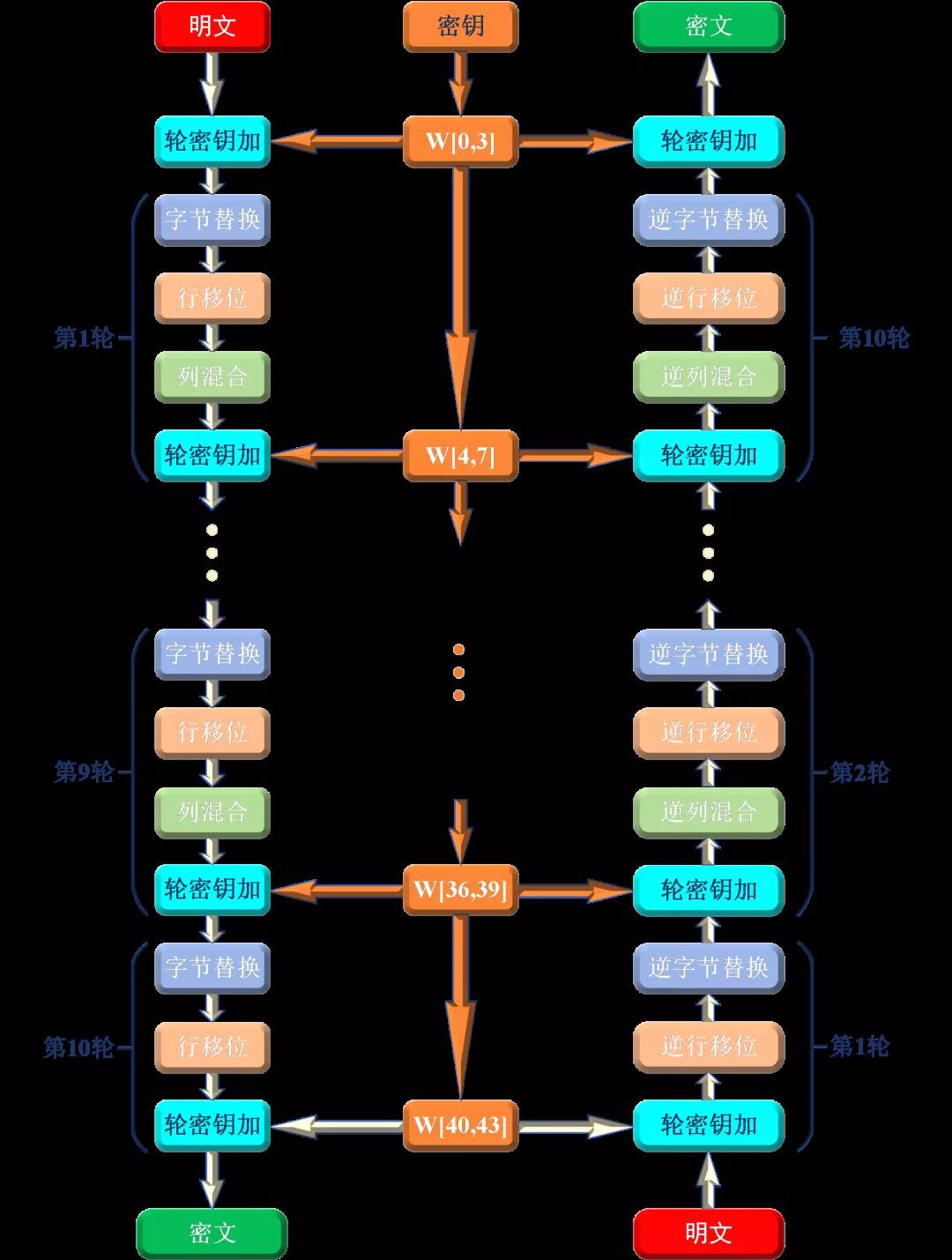

AES数据加密/破译步骤如下图2.1所显示,以“AES-128”方式为例子。

数据加密全过程中第1至9轮的实际操作完全一致,轮函数公式由四个流程构成:字节数更换、行偏移、列混和、轮密匙加,第10轮沒有列混和这一阶段。在其中函数公式是密匙生产调度的一个函数公式[7]。

图2.1 AES数据加密/破译流程表

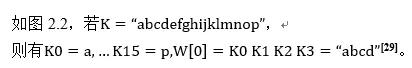

图2.2 密匙分类

2.2.1 字节数更换

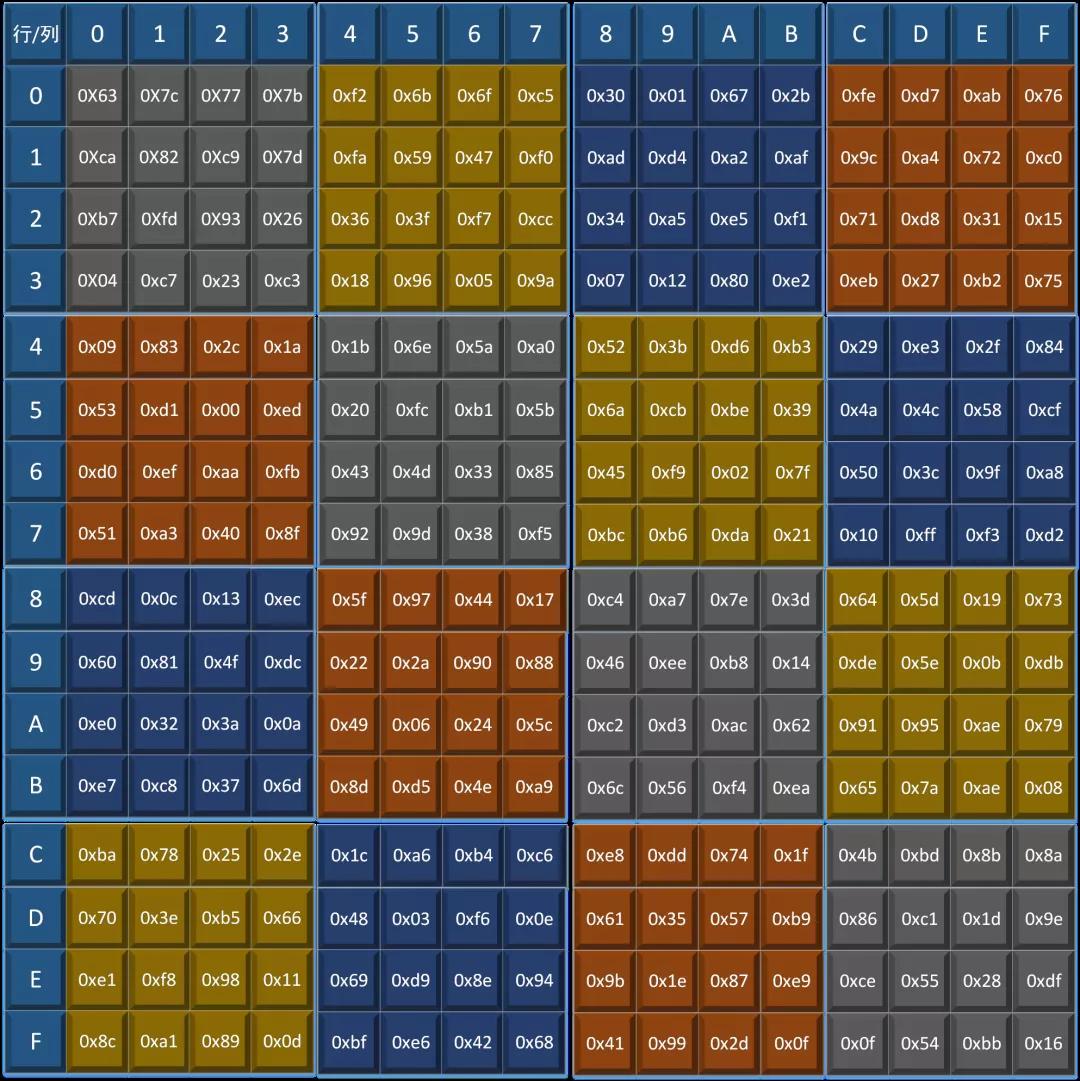

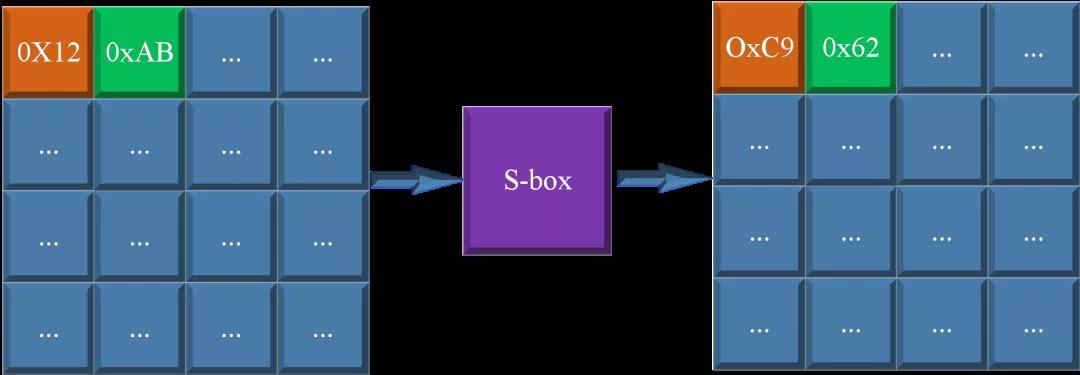

字节数更换(SubBytes( ))是单独的最优控制字节数更换,应用S-box对情况引流矩阵中的每一个字节数开展更换,如下图2.3与2.4。S-box根据RAM完成[13]是可逆性的,做为字节数代用的“搜索表”,情况引流矩阵中的原素(字节数)在开展更换时,可将该字节数的高4bits当作“行座标”,低4bits做为“列座标”,将相匹配座标的值做为更换后的值輸出。例如数据加密时情况引流矩阵輸出的字节数为0xAB(左侧),则查S盒的第0xA行和0xB列,获得数值0x62(右侧),随后用0x62更换原来的0xAB[7,29]。

图2.3 S-box

图2.4情况引流矩阵的字节数更换全过程

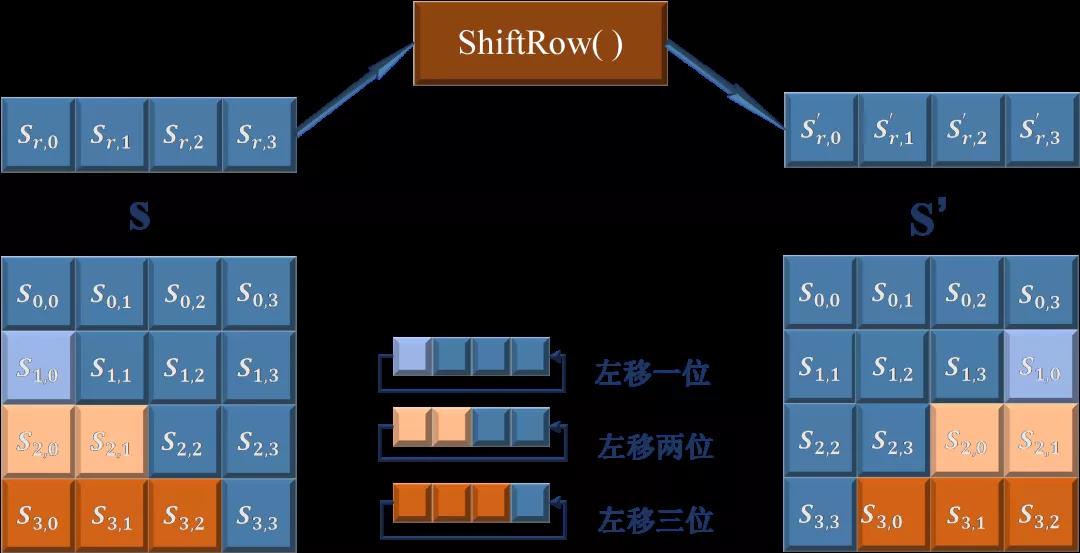

2.2.2 行挪动

如下图2.5所显示,内行转换(ShiftRow( ))中,情况引流矩阵的第2、3、4行字节数是循环系统的,每排有不一样的偏移。第1行无需挪动,第2行偏移一位,第3行左移二位,第4行偏移三位。

图2.5行变换中循环系统挪动状态矩阵的后三行

2.2.3 列混和

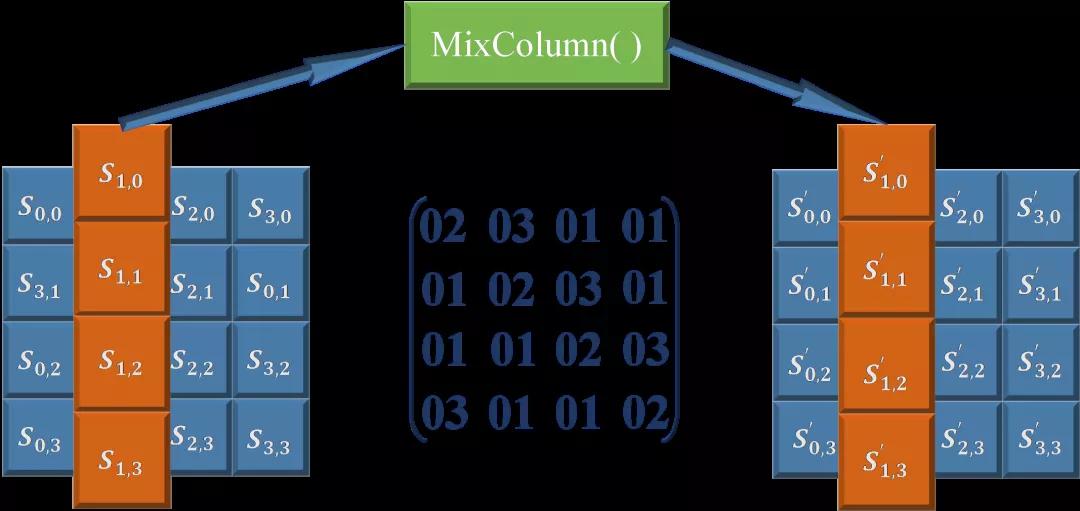

如图2.6,状态矩阵开展列混和(MixColumns( ))变换时,是逐列开展的,每列均会被解决成上的一个4项式,并且用一个相应的矩阵去与该列乘积。

图2.6 状态矩阵中列混和的实际操作

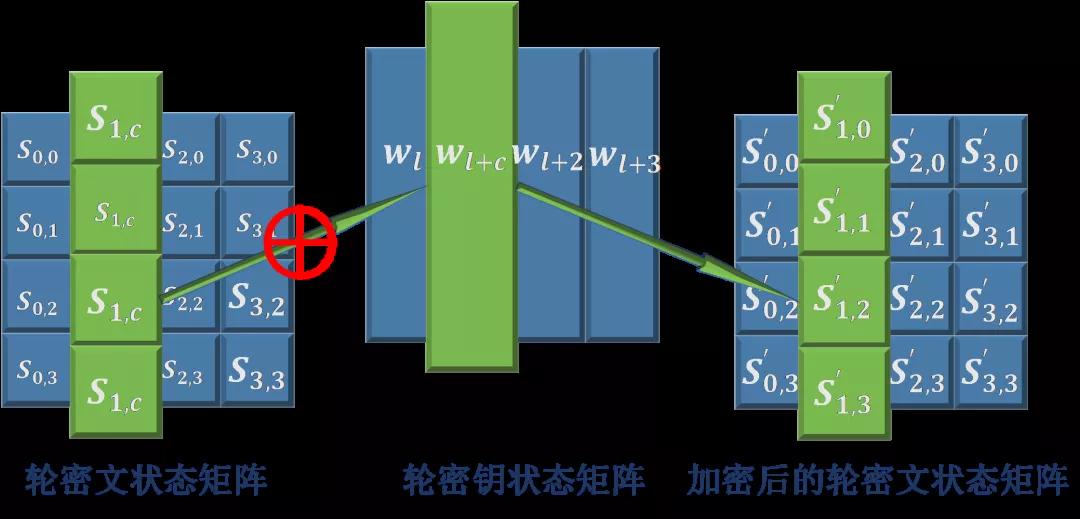

2.2.4 轮密钥加

如图2.1、2.7,轮密钥状态矩阵中的列与轮保密状态矩阵中相匹配的列开展异或运算实际操作(按列开展),转化成新的轮保密状态矩阵,做为下一次数据加密的键入状态矩阵。

图2.7 状态矩阵的轮密钥加变换图

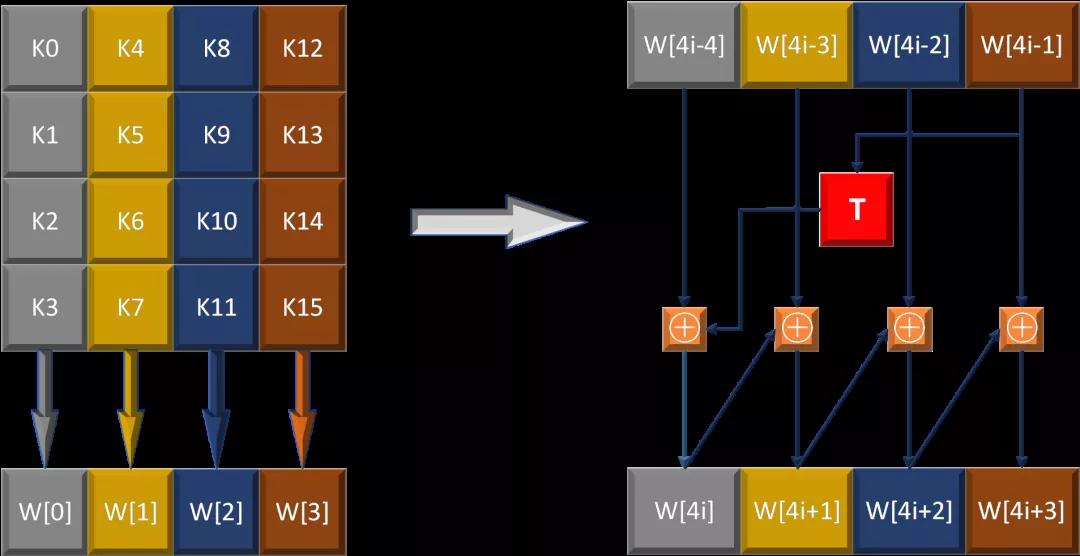

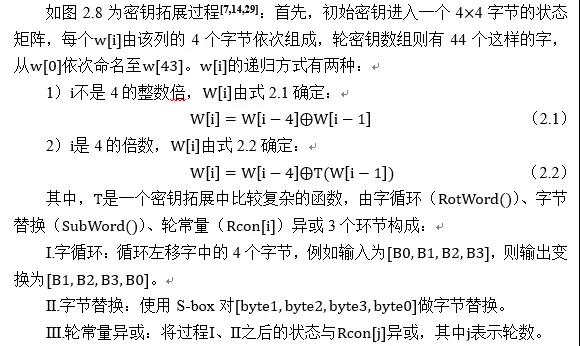

2.3密钥扩展

图2.8 密钥拓展

2.4 AES破译全过程

AES-128破译全过程实质是加锁的逆全过程(如图2.1,2.2),因而破译也必须开展10轮变换,篇数比较有限,这儿不进行详细介绍,实际请论文参考文献[7]。

3AES流水线结构RTL完成

3.1 生产流水线AES电源电路构造

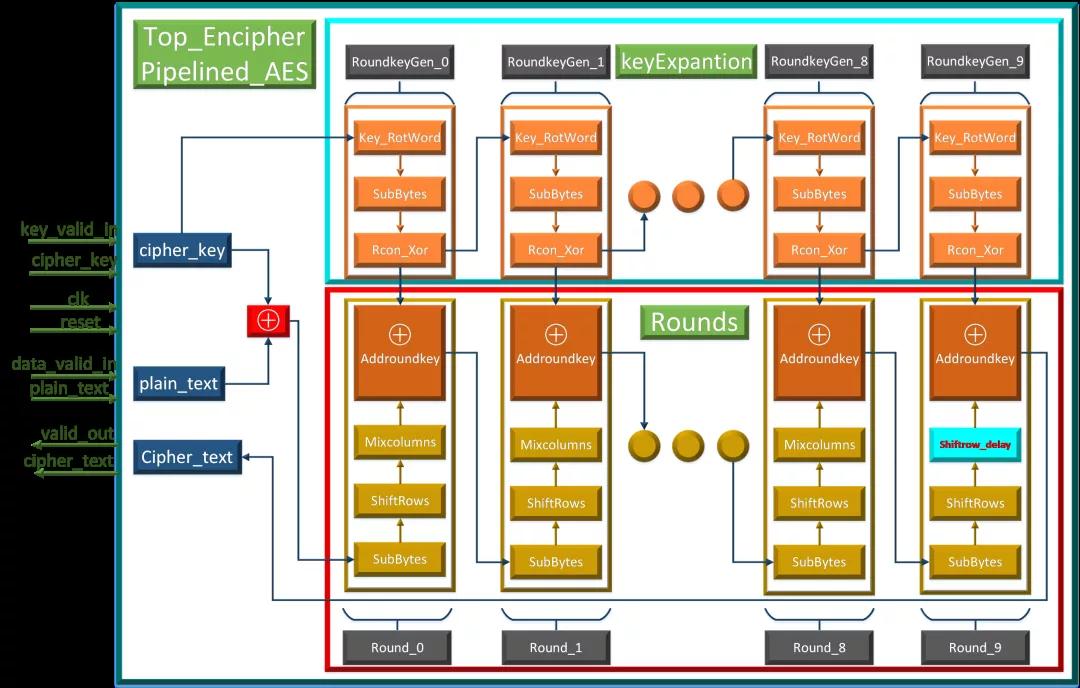

图3.1流水线结构的AES总体框架图

如图3.1所显示,流水线设计将AES的加密与解密独立分离,而且分别做生产流水线解决,关键应用很多的组成逻辑性,选用“放弃总面积获得速率”的对策[7]。

3.2 AES流水线结构数据加密电源电路

如图3.2为流水线结构AES数据加密电源电路,现对其端口号数据信号表明,如表3.1:

表3.1 数据加密模块端口号数据信号

图3.2 流水线结构AES数据加密电源电路控制模块图

AES-128必须数据加密梯度下降法10轮(Round_0至Round_9),在迭代以前,键入的128bits密文会与原始的128bits密钥开展AddRoundKey( )(轮密钥加)实际操作,其結果会做为梯度下降法的第一轮(Round_0)键入;从第1-9轮每场的变换顺序与流程同样,第1轮列混和形成的状态矩阵会与第1轮造成的轮密钥开展异或运算,其计算結果会做为第2轮的键入,依此类推;第10轮则少一个列混和的阶段,可是为了能和其他轮的使用時间两端对齐,促使其結果和第10轮造成的轮密钥异或运算不容易出差错,因此刻意应用一个存储器Shiftrow_delay延迟一拍来替代少了的列混和阶段,那样从Shiftrow_delay出去的結果再开展轮密钥加时赛,就恰好与第10轮造成的轮密钥两端对齐(在某种程度上可以合理的避免侧频带进攻)[7]。

KeyExpantion是密钥扩展控制模块,它也是必须10轮计算(RoundkeyGen_0至RoundkeyGen_9),它每场都先后开展三个流程:Rotword()、SubByte()、Rcon[j]异或运算,在第1到第9轮,每场密钥在开展轮变量定义异或运算完以后出现的状态矩阵会与数据信息列混和以后的状态矩阵开展异或运算实际操作,第10轮则是密钥的轮变量定义异或运算完的状态矩阵与信息的延迟存储器出去的状态矩阵开展异或运算,这时会拉升valid_out数据信号,輸出保密[7]。

破译电路原理请论文参考文献[7]。

3.3 特性评定

根据FPGA的检测与认证,选用tt28nm加工工艺对该设计方案实现综合性,流水线结构的AES设计方案总面积为0.17mm2,这大概是循环系统梯度下降法构造(0.018mm2)的10倍,这也是意料之中的結果。该构造的AES数据信息从键入到存储器的关键线路用时为0.39ns,从存储器到輸出的关键线路用时也是0.39ns,因而理论上该构造的较大頻率为:1GHz/0.39ns=2.56GHz[7]。

【总结】

文中简单介紹了一种AES的流水线结构的IP核设计方法,现阶段使用的是与CPU同宗同屏[2]的钟表,自然,强烈推荐与CPU钟表做多线程解决,而且相互配合DMA(Direct Memory Access,立即储存器浏览 )应用,这会促使AES工作中在贴近本身较大頻率(自然这也是一个功能损耗与效率的最合适的),进而可以最大限度地减轻CPU的工作压力,进一步的提高货运量与数据加密高效率。

论文参考文献

[1] 科普中国. IP核. [EB/OL].https://baike.baidu.com/item/

IP核#reference-[1]-677617-wrap

[2] Mohit Arora. The Art of Hardware Architecture: Design Methods and Techniques for Digital Circuits[M]. 李海东,来萍,师谦等译. 北京市:机械工程出版社出版,2014.2

[3] Michael D Ciletti. Verilog HDL高級数字设计[M]. 张雅绮,译. 北京市:电子工业出版社出版,2005

[4] ZainalabedinNavabi. Verilog HDL数字设计与综合性[M]. 夏宇闻,译. 北京市:电子工业出版社出版,2009

[5] J Bhasker. Verilog HDL新手入门[M]. 夏宇闻,译. 北京市:北航出版社出版,2008

[6] 蔡觉平.Verilog HDL数字集成电路高級编程设计[M].西安市:西安电子科技大学出版社出版,2015.

[7] 马浩. 性能卓越CPU安全性控制模块的制定与提升[D]. 西安市:西安电子科技大学研究生论文,2020.

[8] 张春生, 朝向SOPC的IP核设计方案与IP核复用技术科学研究[D].长沙市:国防科大毕业生论文,2006:7-10.

[9] 梁颖. SOPC中FPGA IP核配备计划方案分析与完成[D].西安市:西安电子科技大学毕业生论文,2010:5-8.

[10] 孙涛. IP软核认证方式科学研究[D].北京市:北京交通大学毕业生论文,2009:5-13.

[12] 任爱锋,罗丰,宋士权等.根据FPGA的嵌入式操作系统设计方案[M].西安市:西安电子科技大学出版社出版,2014:100-114.

[13] 戴强,戴紫彬,李勇.根据加强型延迟认知CSE优化算法的AES S盒电源电路可靠性设计[J].电子学报,2019,47(01):129-136.

[14] Secretary of Commerce. Federal Information Processing Standards Publication-197-2001. ADVANCED ENCRYPTION STANDARD (AES) [S]. America:National Institute of Standards and Technology (NIST),2001.Available at http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf

[15] 谷利泽,郑世慧,杨义先.现代密码学实例教程(第2版)[M].北京市:北京邮电大学出版社出版,2015:73-85.

[16] 郑东,赵庆兰,张应辉.密码算法具体描述[J].西安邮电大学学刊,2013,18(06):1-10.

[17] 胡往东,魏琴芳,胡蓉.应用密码学(第3版)[M].北京市:清华大学出版社,2014:108-130.

[18] Celio, Christopher and Patterson, et al. The Berkeley Out-of-Order Machine (BOOM): An Industry-Competitive, Synthesizable, Parameterized RISC-V Processor[R], EECS Department, University of California, Berkeley, June 2015.

[19] Christopher Celio, David Patterson, and Krste Asanovi′c, The Berkeley Out-of-Order Machine (BOOM) Design Specification[R],EECS Department, University of California, Berkeley,December 2016.

[20] Gavin Ferris, Robert Mullins, Wei Song et al. Open source 64-bit SoC[EB/OL],

https://www.lowrisc.org/, 2020-3

[21] PULPino User Manul[EB/OL], http://www.pulp-platform.org/documentation/, 2016-8

[22] Russia GNSS Sensor Company, RISC-V VHDL: System-on-chip[EB/OL],

https://github.com/sergeykhbr/riscv_vhdl/, 2020-3

[23] Christopher Schmitz,Sebastian Pape. LiSRA: Lightweight Security Risk Assessment for decision support in information security[J]. Computers & Security,2020,90.

[24] 刘阳.2019年海外网络信息安全趋势具体描述[J].信息保密科技进步,2019(12):8-13.

[25] 张焕国,林西岱,马建峰等.网络空间安全具体描述[J].中国科学:计算机科学,2016,46(02):125-164.

[26] 雷新锋,宋书民,薛锐等.测算靠谱的登陆密码协议书流于形式剖析具体描述[J].计算机学报,2014,37(05):

993-1016.

[27] 冯登国,徐静,兰晓.5G移动通信技术网络信息安全科学研究[J].软件学报,2018,29(06):1813-1825.

[28] 洪泽,洪锋,陈振娇.对于车联网平台网络信息安全的数据加密模块ic设计[J].网络安全与运用,2020(02):36-38.

[29] TimeShatter. AES加密技术的详解与完成[EB/OL]. https://blog.csdn.net/qq_28205153/

article/details/55798628.html/2017-02-19

[30] J.Daemen, V.Rijmen著.高級数据加密规范(AES)优化算法:Rijndael的设计方案[M].谷大武,徐胜波译,北京市:清华大学出版社,2003:216-220